УДК 681.01:519.713

В.А. Краснобаев<sup>1</sup>, С.А. Кошман<sup>2</sup>, А.И. Тыртышников<sup>1</sup>, Н.С. Гаркавенко<sup>1</sup>

$^1$ Полтавский национальный технический университет имени  ${\it Ю}$ рия  ${\it К}$ ондратюка, Полтава

# КОНЦЕПЦИЯ СОЗДАНИЯ ОТКАЗОУСТОЙЧИВЫХ КОМПЬЮТЕРНЫХ СИСТЕМ ОБРАБОТКИ ИНФОРМАЦИИ В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ НА ОСНОВЕ ПРИМЕНЕНИЯ ПЛИС

В данной статье предложена концепция создания отказоустойчивых компьютерных систем обработки информации, функционирующих в системе остаточных классов (СОК). При этом предлагается реализовать компьютерную систему на ПЛИС. Полученные результаты свидетельствуют о высокой эффективности использования СОК при реализации модульных арифметических операций.

**Ключевые слова:** системы обработки информации, система остаточных классов, пользовательская производительность, отказоустойчивость, программируемые логические интегральные схемы.

## Введение

Поиски путей повышения пользовательской производительности и отказоустойчивости компьютерных систем обработки информации (КСОИ) являются важной и актуальной задачей.

Существуют различные пути повышения производительности КСОИ. Одни методы повышения производительности основываются на применении многомашинных комплексов и многопроцессорных систем. Использование данных методов, повышая системную производительность, оставляет значение пользовательской производительности в одних и тех же пределах. Более перспективными путями повышения производительности КСОИ являются методы, основанные на использовании некоторых свойств (естественный параллелизм смежных операций, естественный параллелизм независимых ветвей решаемого алгоритма, параллелизм множества объектов и т.п.) задач определённого класса, а также методы, позволяющие искусственно распараллелить некоторые вычислительные алгоритмы. Применение данных методов позволяет существенно повысить производительность КСОИ, однако сфера применения их ограничивается классом решаемых задач. Кроме этого сам процесс искусственного расчленения алгоритмов, определения и выделения независимых ветвей требует больших трудозатрат, причём не всегда и возможно распараллеливание произвольных алгоритмов вообще. Все перечисленные пути повышения производительности КСОИ обладают общим недостатком: невозможность распараллелить решаемые алгоритмы на уровне элементарных операций (микроопераций).

Развитие современной микроэлектронной базы и в частности широкое применение больших и

сверхбольших интегральных схем дало толчок к исследованию возможности применения табличных методов обработки информации. Применение табличных методов обработки информации может обеспечить высокую производительность (за счёт возможности распараллелить элементарную операцию) и надёжность, а также обуславливает высокую степень регулярности и однородности структуры устройств для их реализации. Существенными недостатками (которые обуславливают трудность, а в некоторых случаях и невозможность их практической реализации) табличных методов переработки информации, применяемых в позиционных системах счисления (ПСС), остаётся значительное количество необходимого оборудования.

В литературе [1] показано, что одним из действенных путей решения данной проблемы является применение в качестве системы счисления КСОИ непозиционной системы счисления в остаточных классах (СОК).

Применение СОК позволяет достичь хороших результатов в области создания современных КСОИ. Так, СОК может эффективно использоваться в оптоэлектронных матричных и векторных процессорах обработки данных, при решении задач цифровой фильтрации, решении задач дискретного преобразования Фурье, решения задач распараллеливания вычислений для криптографических систем и задач оптимизации математических вычислений в полях Галуа, векторных и сигнальных вычислениях и пр. Это обусловлено тем, что, во-первых, для решения вышеперечисленного класса задач требуется реализация модульных арифметических операций, как правило, для большой разрядной сетки КСОИ; вовторых, требуется обеспечить высокую пользовательскую производительность вычислений; в-треть-

<sup>&</sup>lt;sup>2</sup> Харьковский национальный технический университет сельского хозяйства имени Петра Василенко, Харьков

их, базовой операцией при таких вычислениях является операция модульного умножения или операции вида вычислений суммы попарных произведений и им подобных. Данное обстоятельство и позволяет эффективно использовать принципы реализации арифметических операций в СОК для решения вышеприведённых вычислительных задач.

В СОК операнд A представляется в виде набора остатков  $\{a_i\}$ ,  $i=\overline{1,n}$ , от деления числа на набор  $\{m_i\}$  модулей (оснований), при условии, что они взаимно попарно простые числа, т.е. для любой пары оснований наибольший общий делитель равен единице:  $(m_i,m_j)=1; i\neq j$ , где  $a_i=A-[A/m_i]m_i$ . В этом случае арифметические операции сложение, вычитание и умножение выполняют по каждому из модулей  $m_i$  независимо друг от друга и параллельно во времени, т. е. алгоритм реализации обобщённой арифметической операции  $\otimes$  представляется в виде  $C=A\otimes B=(a_1,a_2,...,a_n)\otimes (b_1,b_2,...,b_n)==(c_1,c_2,...,c_n)$ , где  $c_i=(a_i\otimes b_i)$  mod  $m_i$ .

К данному моменту времени существует достаточно много теоретических разработок вариантов создания структуры КСОИ в СОК. Так, при этом в табличном варианте синтеза операционного устройства (ОУ) КСОИ результат арифметической операции определяется в момент поступления входных операндов, т.е. за один такт.

Исходя из основных свойств СОК (малоразрядность, независимость и равноправность остатков), можно определить основные особенности синтеза блоков и узлов КСОИ в СОК.

- 1. ОУ КСОИ в СОК состоит из отдельно функционирующих трактов обработки данных (ТОД). Каждый ТОД функционирует независимо друг от друга и параллельно во времени.

- 2. ОУ КСОИ СОК состоит из n последовательных вычислителей, где n количество оснований СОК. Каждый вычислитель работает в  $k = \lceil \log_2 \left(m-1\right) \rceil + 1$  разрядной сетке.

- 3. Малоразрядность остатков, представляющих операнд в СОК, позволяет реализовать арифметические операции как на базе малоразрядных двоичных сумматоров, так и на базе ПЗУ, выполненных в табличном (матричном) варианте. Данное обстоятельство существенно влияет на время выполнения арифметических операций в КСОИ.

- 4. Блочное построение ОУ КСОИ в СОК позволяет локализовать ошибки (или группы ошибок, не превышающих значение  $k = \lfloor \log_2(m-1) \rfloor + 1$ ) в одном тракте вычислителя [2]. Эта особенность позволяет создать систему контроля и коррекции ошибок, не прерывая решения задачи (алгоритма), т. е.

производить коррекцию ошибок в динамике вычислительного процесса.

Для проверки теоретических выводов и расчетов целесообразно решить задачу построения ОУ КСОИ в СОК.

# Результаты исследований

В данной статье ставится задача машинного синтеза ОУ КСОИ в СОК на основе использования языка программирования аппаратуры AHDL.

В качестве исходных данных для решения задачи синтеза ОУ КСОИ в СОК принимаем:

- величина разрядной сетки ОУ КСОИ в СОК 8 двоичных разрядов (  $\ell=1$  );

- техническая реализация ОУ будет производиться на основе использования программируемых логических интегральных схем (ПЛИС);

- принцип реализации арифметических операций табличный;

- тип реализуемых ОУ КСОИ в СОК операций

сложение, вычитание, умножение.

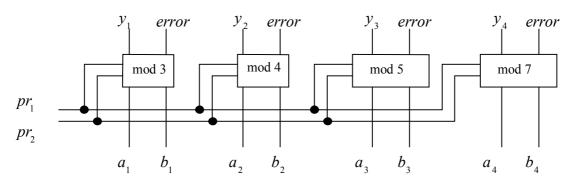

В соответствии с исходными данными, структура ОУ КСОИ в СОК для  $\ell=1$  представлена на рис. 1.

Структурная схема включает в себя четыре вычислительных тракта, функционирующих независимо друг от друга и параллельно во времени по соответствующим модулям  $m_1=3$ ,  $m_2=4$ ,  $m_3=5$ ,  $m_4=7$ . Каждый из модулей имеет информационные входы  $a_i$ ,  $b_i$  и выход  $y_i$ , а также выход еггог, который сигнализирует о возникновении некорректных (ошибочных) ситуаций на входе  $pr_i$  (вход признака входа реализуемой операции).

Спроектированный процессор реализован на ПЛИС семейства МАХЗ000А, в основе архитектуры которой лежат логические блоки, макроячейки, логические расширители (параллельный и разделяемый), программируемая матрица соединений, элементы ввода-вывода, что является практически идеальной базой для реализации модульного принципа построения структуры ОУ и основным методам реализации арифметических операций в СОК, выполнение которых базируется на её основных свойствах.

ПЛИС имеют четыре вывода, закреплённых за глобальными цепями. Это глобальные цепи синхронизации сброса и установки в третье состояние каждой макроячейки.

Логические блоки, состоящие из 16 макроячеек каждый, соединяются с помощью программируемой матрицы соединений. Каждый логический блок имеет 36 входов с программируемой матрицей соединений.

Макроячейка ПЛИС семейства MAX3000A состоит из трёх основных узлов:

- локальной программируемой матрицы;

- матрицы распределения термов;

– программируемого регистра.

Для реализации логических функций большого числа переменных используются логические расширители. Разделяемый логический расширитель позволяет реализовать логическую функцию с большим числом входов, позволяя объединить макроячейки, входящие в состав одного логического блока. Параллельный логический расширитель позволяет использовать локальные матрицы смежных макроячеек для реализации функций, в которые входят более 5 термов.

На программируемую матрицу соединений выводятся сигналы от всех возможных источников: элементов ввода-вывода, сигналов обратной связи логических блоков, специализированных выделенных выводов. В процессе программирования только необходимые сигналы подаются на каждый логический блок. Элементы ввода-вывода позволяют организовать режимы работы с открытым коллектором и третьим состоянием.

Выбор микросхемы осуществлялся посредством системы автоматизированного проектирования, поставляемой фирмой Altera - MAX+plusII, на основе разработанной программы функционирования ОУ КСОИ в СОК. Микросхема EPM3064ATC100-4 выбрана из семейства MAX3000A. Основные пара-

метры микросхемы ЕРМ3064А приведены в табл. 1.

Количество входов микросхемы — 22, выходов — 14. В целом ресурсы микросхемы используются на 68%, что даёт возможность их дополнительного использования для улучшения отдельных свойств (в частности отказоустойчивости и надежности) ОУ КСОИ в СОК.

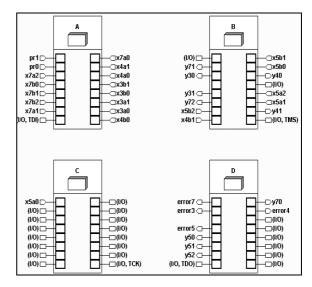

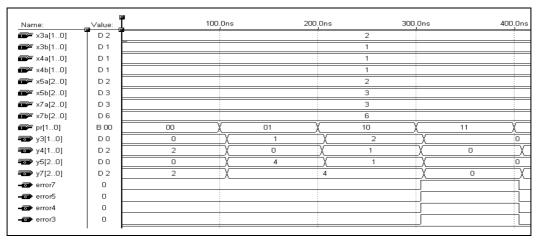

Микросхема состоит из 4-х логических блоков A, B, C, D (рис. 2). Логические блоки задействованы на 44%. Временная диаграмма функционирования синтезированного ОУ приведена на рис. 3.

В соответствии с данной диаграммой можно проанализировать процессы реализации арифметических операций ОУ КСОИ в СОК. Рассмотрим пример для конкретных значений операндов  $A_{17} = (2,1,2,3)$  и  $B_{13} = (1,1,3,6)$ .

Полученные результаты синтеза однобайтового ОУ КСОИ в СОК могут быть использованы для построения КСОИ в СОК для произвольной  $\ell$  - байтовой разрядной сетки для  $\ell \geq 2$ , которые можно рекомендовать для использования в качестве арифметических расширителей базовых вычислительных систем, в частности, для реализации алгоритмов

вида

$$\sum_{i=1}^{n} a_i b_i$$

и им подобных.

Рис. 1. Структурная схема операционного устройства спецпроцессора в СОК

# Таблица 1 Основные параметры микросхемы EPM3064A

| Наименование<br>параметра               | Значения<br>параметров |  |  |  |

|-----------------------------------------|------------------------|--|--|--|

| Логическая ёмкость, эквивалентных       | 10.50                  |  |  |  |

| вентилей                                | 1250                   |  |  |  |

| Число макроячеек                        | 64                     |  |  |  |

| Число логических блоков                 | 4                      |  |  |  |

| Задержка распространения сигнала        |                        |  |  |  |

| вход-выход, t <sub>PD</sub> , [нс]      | 4,5                    |  |  |  |

| Время установки глобального тактово-    |                        |  |  |  |

| го сигнала, t <sub>SU</sub> , [нс]      | 3                      |  |  |  |

| Задержка глобального тактового сиг-     |                        |  |  |  |

| нала до выхода, t <sub>CO1</sub> , [нс] | 2,8                    |  |  |  |

| Максимальная глобальная тактовая        |                        |  |  |  |

| частота, $f_{CNT}$ , [М $\Gamma$ ц]     | 192,3                  |  |  |  |

Рис. 2. Логические блоки микросхемы

Рис. 3. Временная диаграмма функционирования СП

Таблица 2

Время задержек реализации арифметических операций

|      | error3 | error4 | error5 | error7 | y30         | y31         | y40   | y41         | y50         | y51         | y52         | y70   | y71   | y72   |

|------|--------|--------|--------|--------|-------------|-------------|-------|-------------|-------------|-------------|-------------|-------|-------|-------|

| pr0  | 4,7ns  | 4,7ns  | 4,7ns  | 4,7ns  | 7,8ns       | 6,5ns\7,8ns | 4,7ns | 6,5ns\7,8ns | 6,5ns\7,8ns | 6,5ns\7,8ns | 6,5ns\7,8ns | 7,8ns | 7,8ns | 7,Bns |

| pr1  | 4,7ns  | 4,7ns  | 4,7ns  | 4,7ns  | 6,5ns\7,8ns | 6,5ns\7,8ns | 4,7ns | 6,5ns\7,8ns | 6,5ns\7,8ns | 6,5ns\7,8ns | 6,5ns\7,8ns | 7,8ns | 7,8ns | 7,8ns |

| x3a0 |        |        |        |        | 6,3ns\7,8ns | 6,3ns\7,8ns |       |             |             |             |             |       |       |       |

| x3a1 |        |        |        |        | 6,3ns\7,8ns | 6,3ns\7,8ns |       |             |             |             |             |       |       |       |

| x3b0 |        |        |        |        | 6,3ns\7,8ns | 6,3ns\7,8ns |       |             |             |             |             |       |       |       |

| x3b1 |        |        |        |        | 6,3ns\7,8ns | 6,3ns\7,8ns |       |             |             |             |             |       |       |       |

| x4a0 |        |        |        |        |             |             | 4,5ns | 7,6ns       |             |             |             |       |       |       |

| x4a1 |        |        |        |        |             |             |       | 4,5ns\7,6ns |             |             |             |       |       |       |

| x4b0 |        |        |        |        |             |             | 4,5ns | 6,3ns\7,6ns |             |             |             |       |       |       |

| x4b1 |        |        |        |        |             |             |       | 6,3ns\7,6ns |             |             |             |       |       |       |

| x5a0 |        |        |        |        |             |             |       |             | 6,3ns\7,6ns | 6,3ns\7,6ns | 6,3ns\7,6ns |       |       |       |

| x5a1 |        |        |        |        |             |             |       |             | 6,3ns\7,6ns | 6,3ns\7,6ns | 6,3ns\7,6ns |       |       |       |

| x5a2 |        |        |        |        |             |             |       |             | 6,3ns\7,6ns | 6,3ns\7,6ns | 6,3ns\7,6ns |       |       |       |

| x5b0 |        |        |        |        |             |             |       |             | 6,3ns\7,6ns | 6,3ns\7,6ns | 6,3ns\7,6ns |       |       |       |

| x5b1 |        |        |        |        |             |             |       |             | 6,3ns\7,6ns | 6,3ns\7,6ns | 6,3ns\7,6ns |       |       |       |

| x5b2 |        |        |        |        |             |             |       |             | 6,3ns\7,6ns | 6,3ns\7,6ns | 6,3ns\7,6ns |       |       |       |

| x7a0 |        |        |        |        |             |             |       |             |             |             |             | 7,7ns | 7,7ns | 7,7ns |

| x7a1 |        |        |        |        |             |             |       |             |             |             |             | 7,7ns | 7,7ns | 7,7ns |

| x7a2 |        |        |        |        |             |             |       |             |             |             |             | 7,7ns | 7,7ns | 7,7ns |

| x7b0 |        |        |        |        |             |             |       |             |             |             |             | 7,7ns | 7,7ns | 7,7ns |

| x7b1 |        |        |        |        |             |             |       |             |             |             |             | 7,7ns | 7,7ns | 7,7ns |

| x7b2 |        |        |        |        |             |             |       |             |             |             |             | 7,7ns | 7,7ns | 7,7ns |

#### Заключение

Сделаем следующие основные выводы:

на основании использования программы MAX+plusII был синтезирован однобайтовый процессор в СОК на языке AHDL;

- выбрана микросхема EPM3064ATC100-4, на которой реализован процессор;

- получены времена задержек реализации каждой из арифметических операций, которые приведены в табл. 2; полученные результаты подтверждают теоретические исследования эффективности использования СОК для построения быстродействующих процессоров обработки цифровой информации.

Таким образом, очевидна целесообразность использования непозиционной системы счисления в СОК для построения отказоустойчивых и быстродействующих КСОИ.

### Список литературы

- 1. Акушский И.Я. Машинная арифметика в остаточных классах / И.Я. Акушский, Д.И. Юдицский. – М.: Сов. радио, 1968. – 444 с.

- 2. Материалы Международной научно-технической конференции "50 лет модулярной арифметике". МИЭТ, г. Зеленоград. Моск. обл. 23-25 ноября 2005г.

Поступила в редколлегию 31.07.2013

**Рецензент:** д-р техн. наук, проф. В.М. Илюшко, Национальный аэрокосмический университет им. Н.Е. Жуковского "ХАИ", Харьков.

#### КОНЦЕПЦІЯ СТВОРЕННЯ ВІДМОВОСТІЙКИХ КОМП'ЮТЕРНИХ СИСТЕМ ОБРОБКИ ІНФОРМАЦІЇ У СИСТЕМІ ЗАЛИШКОВИХ КЛАСІВ НА ОСНОВІ ЗАСТОСУВАННЯ ПЛІС

В.А. Краснобаєв, С.О. Кошман, О.І. Тиртишніков, М.С. Гаркавенко

У даній статті запропонована концепція створення відмовостійких комп'ютерних систем обробки інформації, що функціонують у системі залишкових класів (СЗК). При цьому пропонується реалізувати комп'ютерну систему на ПЛІС. Отримані результати свідчать про високу ефективність використання СЗК при реалізації модульних арифметичних операцій.

**Ключові слова**: системи обробки інформації, система залишкових класів, користувацька продуктивність, відмовостійкість, програмовані логічні інтегральні схеми.

# THE CONCEPT OF CREATING FAULT-TOLERANT COMPUTER SYSTEMS FOR DATA PROCESSING IN THE SYSTEM OF RESIDUAL CLASSES BASED ON THE USE OF PLD

V.A. Krasnobaev, S.A. Koshman, A.I. Tyrtyshnikov, N.S. Harkavenko

In this article the concept of a fault-tolerant computer systems information processing is proposed which functioning in system of residual classes (SRC). It is proposed to implement this computer system on the PLD. The results indicate the high efficiency of SRC in the implementation of the modular arithmetic operations.

**Keywords**: information processing system, system of residual classes, user productivity, fault tolerance, programmable logic device.